# TDPA4220QFN

# Wideband (0.5 GHz – 20 GHz) Medium Power Amplifier

### **Product Overview**

The TDPA4220QFN distributed, is а wideband, Driver Amplifier designed for a wide range from UHF to K-band applications, such as electronic warfare, point-to-point Radio, and test instrumentation.

The MPA driver operate over frequency bands of 0.5 to 20 GHz and provides 17 dB of linear gain while providing a typical output power of 20 dBm at 1dB gain compression.

The amplifier is manufactured in a 0.25 µm drawn gate length power pHEMT process technology via holes through the substrate, air bridges, and optical gate lithography.

The part is supplied in a leadless surface mount 28-pin 25 mm<sup>2</sup> QFN package. The circuit is ideal for a wide range of microwave and millimeter wave applications and systems.

#### 30 Pout 25 Gain, NF / P1dB, 1 2 01 51 05 2 02 51 05 20 -P1dB (dBm) ····Linear Gain (dB) -- Psat (dBm) -NF(dB) 0 10 12 16 18 20 22 0 2 6 8 14 FREQUENCY (GHz)

### TELEDYNE C2V HIREL ELECTRONICS Everywherevoulook"

### A Teledyne Defense Electronics Company

# Performance

Linear gain: 17 dB P1dB: 20 dBm

Frequency band: 0.5 - 20 GHz

Output power: 20 dBm @1 dBcomp

Psat: 23 dBm

**Features**

- OIP3: 28 dBm

- Noise Figure: 3 dB

- Quiescent bias point: Vd = 8 V, Id = 190 mA

- 28-pin QFN 5 x 5 mm<sup>2</sup>

- MSL Level: 3

### Absolute Maximum Ratings<sup>(1)</sup>

### Tamb.= +25°C

| Symbol | Parameter                                   | Values  | Unit |

|--------|---------------------------------------------|---------|------|

| Vd     | Drain bias voltage                          | 8       | V    |

| ldq    | Drain bias current                          | 170     | mA   |

| Vg1    | Gate bias voltage Vg1                       | -2 to 0 | V    |

| Vg2    | Gate bias voltage Vg2                       | 1 to 2  | V    |

| Pin    | Maximum CW input power overdrive            | 17      | dBm  |

| Tj     | Maximum junction temperature <sup>(2)</sup> | 175     | °C   |

(1) Operation of this device above anyone of these parameters may cause permanent damage.

(2) Thermal resistance channel to ground paddle.

### **Recommended Operating Conditions**

Ta = +25 °C

| Symbol | Parameter              | Min | Тур | Max | Unit |

|--------|------------------------|-----|-----|-----|------|

| Fop    | Frequency range        | 0.5 |     | 20  | GHz  |

| Gain   | Linear gain            |     | 17  |     | dB   |

| NF     | Noise Figure           |     | 3   |     | dB   |

| Pout   | Output power @ 1dBcomp |     | 20  |     | dBm  |

### **Electrical Specifications**

Tamb = +25 °C, Vg1 to be set in order to have Idq = 120 mA, Vg2 = 1.5 V

| Symbol | Parameter                           | Min | Тур | Max | Unit |

|--------|-------------------------------------|-----|-----|-----|------|

| Freq   | Frequency range                     | 0.5 |     | 20  | GHz  |

| G      | Linear gain                         |     | 17  |     | dB   |

| NF     | Noise Figure                        |     | 3   |     | dB   |

| IRL    | Input Return Loss                   |     | 15  |     | dB   |

| ORL    | Output Return Loss                  |     | 18  |     | dB   |

| P-1dB  | Output power @ 1dBcomp              |     | 20  |     | dBm  |

| Psat   | Saturated output power              |     | 23  |     | dBm  |

| OIP3   | Output Third Order Intercept        |     | 28  |     | dBm  |

| ldq    | Quiescent current on Vd             |     | 120 |     | mA   |

| Vd     | Supply voltage on Vd                | 6   | 6.5 | 7   | V    |

| ld     | Drain current @3dB gain compression |     | 140 |     | mA   |

The values are representative of typical "test fixture" measurement as defined on the drawing in paragraph "Proposed Evaluation Board".

### **Temperature Range**

| Symbol | Parameter                   | Min | Тур | Max  | Unit |

|--------|-----------------------------|-----|-----|------|------|

| Та     | Operating temperature range | 40  |     | +95  | °C   |

| Tstg   | Storage temperature range   | 55  |     | +150 | °C   |

# **Product Specification**

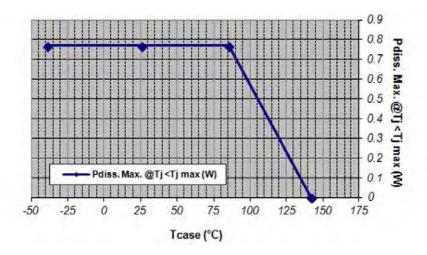

### **Device Thermal Performance**

All the figures given in this section are obtained assuming that the QFN device is cooled down only by conduction through the package thermal pad (no convection mode considered).

The temperature is monitored at the package back-side interface (Tcase) as shown below. The system maximum temperature must be adjusted in order to guarantee that Tcase remains below than the maximum value specified in the next table. So, the system PCB must be designed to comply with this requirement.

A derating must be applied on the dissipated power if the Tcase temperature can not be maintained below than the maximum temperature specified (see the curve Pdiss. Max) in order to guarantee the nominal device life time (MTTF).

The provided thermal information in the next chart is for nominal biasing point: Idq = 110 mA and Vd = 7 V, without RF drive @ Tcase = 85 °C.

| DEVICE THERMAL SPECIFICATION: TDPA4220                          | -QFN      |

|-----------------------------------------------------------------|-----------|

| Recommended max. junction temperature (Ij max)                  | 145 °C    |

| Junction temperature absolute maximum rating                    | 175 °C    |

| Max. continuous dissipated power@Tcase= 85 °C                   | 0.8 W     |

| => Pdiss derating above TcaseC <sup>1</sup> >= 85 °C            | 14 mW/°C  |

| Junction-Case thermal resistance (Rth J-C) <sup>2</sup>         | 73.5 °C/W |

| Min. package back side operating temperature <sup>3</sup> -40°C |           |

| Max. package back side operating temperature <sup>3</sup>       | 85 °C     |

| Min. storage temperature                                        | -55 °C    |

| Max. storage temperature                                        | 150 °C    |

(1 Derating at junction temp constant= Tj max

(2) Rth J-C is calculated for a worse case where the <u>hottest junction</u> of the MMIC is considered.

(3) Tcase=Package back side temperature measured under lhe die-attach-pad (see the drawing below)

Example: QFN 16L 3x3 Location of temperature reference point (Tcase) on package's bottom side

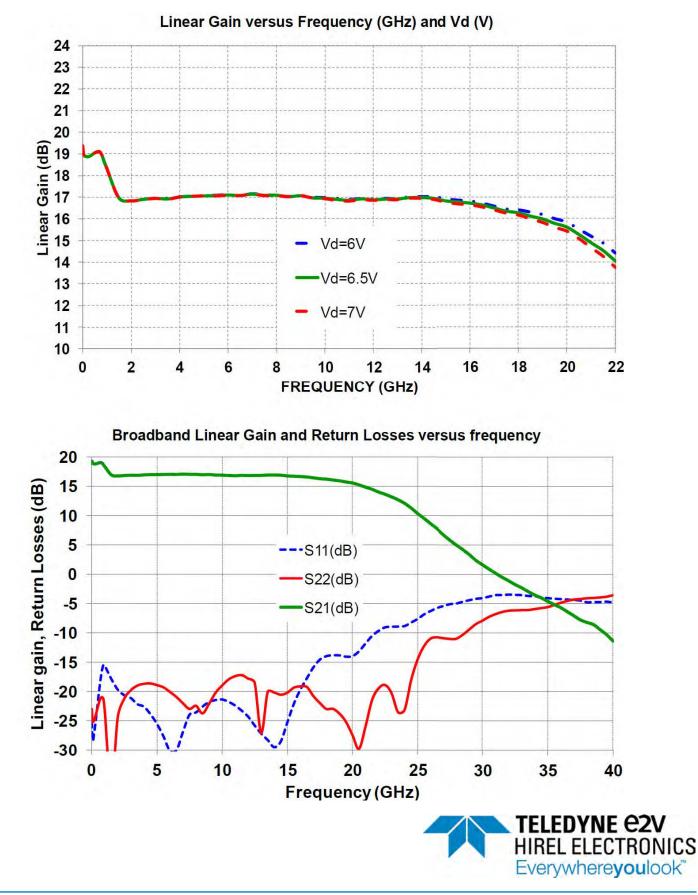

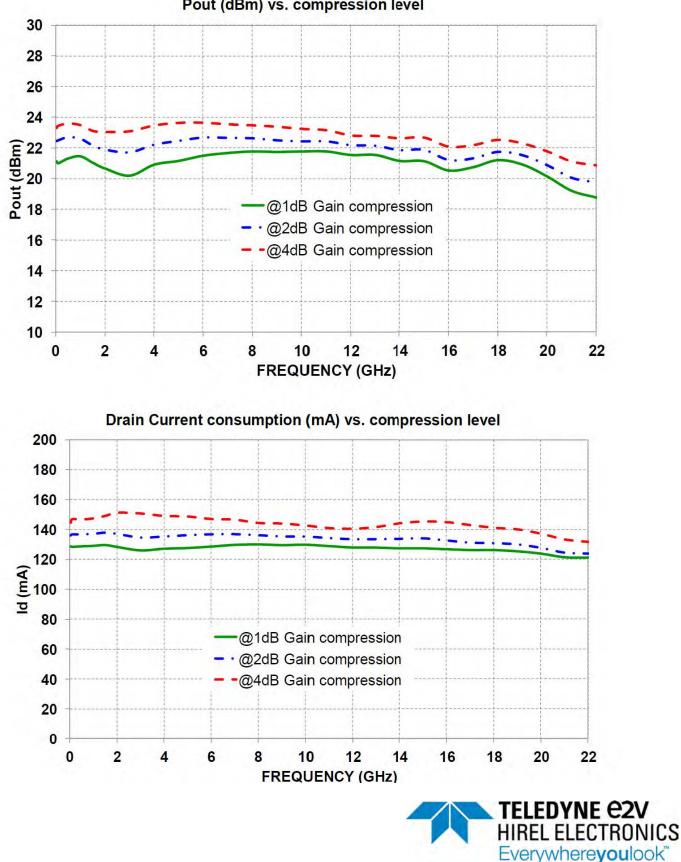

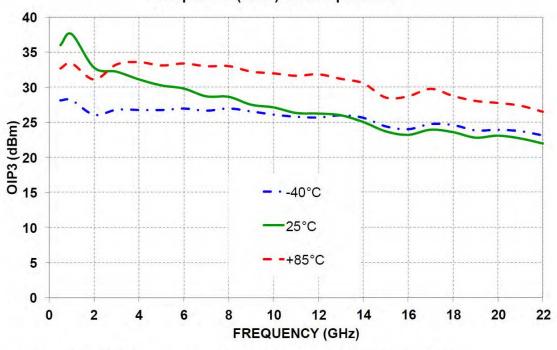

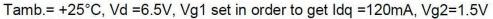

Tamb = +25° C, Vd = 6.5V, Vg1 set in order to get Idq = 120 mA, Vg2 = 1.5 V

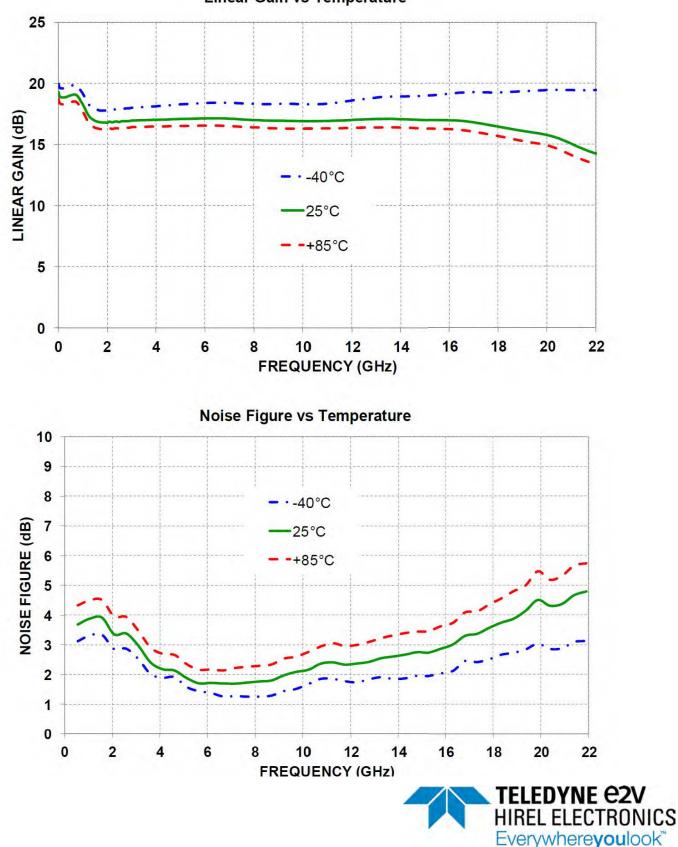

Vd = 6.5 V, Vg1 set in order to get Idq = 120 mA @ Tamb = +25 °C with Vg2 = 1.5 V, Vg1 and Vg2 remain constant versus temperature (Tamb = +25 °C, +85 °C, -40° C)

### Linear Gain vs Temperature

Tamb = +25 °C, Vd = 6.5 V, Vg1 set in order to get Idq = 120 mA, Vg2 = 1.5 V

Vd = 6.5 V, Vg1 set in order to get ldq = 120 mA @ Tamb = +25 °C with Vg2 = 1.5 V Vg1 and Vg2 remain constant versus temperature (Tamb = +25 °C, +85 °C, -40 °C)

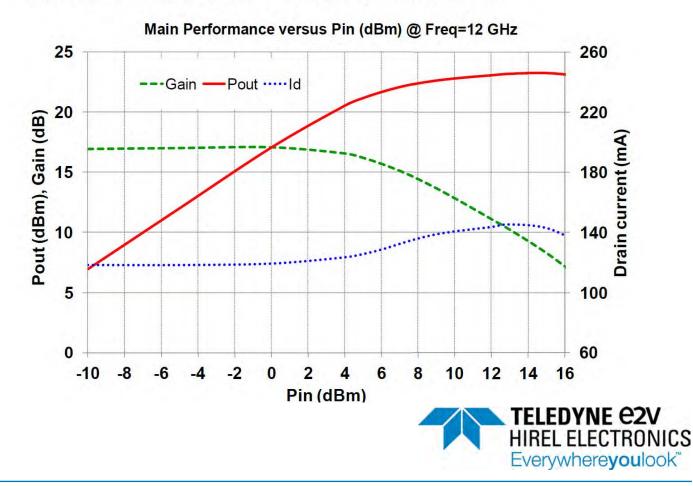

### Package Outline: 28 Lead 5 x 5 QFN<sup>(1)</sup>

<sup>(1)</sup> The package outline drawing included in this data sheet is provided for indication purposes.

<sup>(2)</sup> It is strongly recommended to ground all pins marked "Gnd" through the PCB board. Ensure that the PCB board is designed to provide the best possible ground to the package.

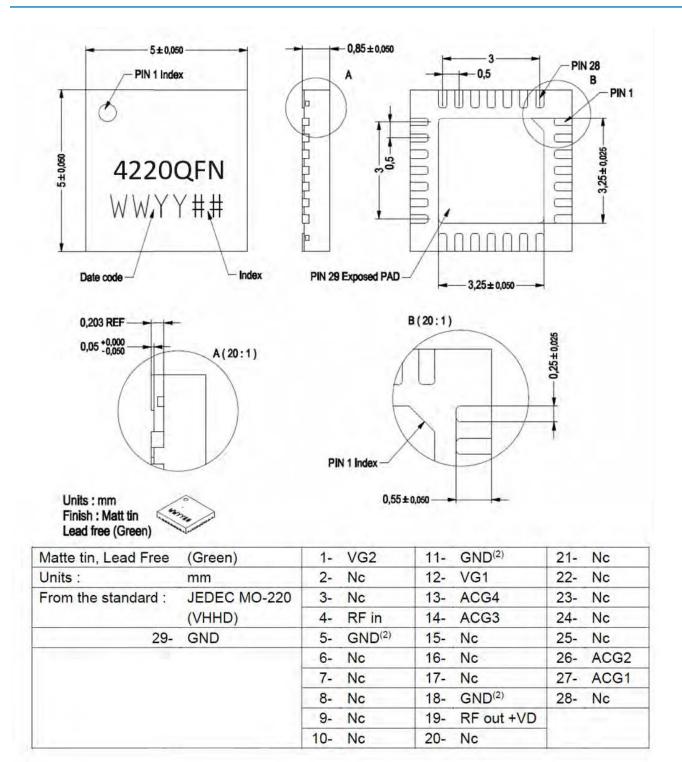

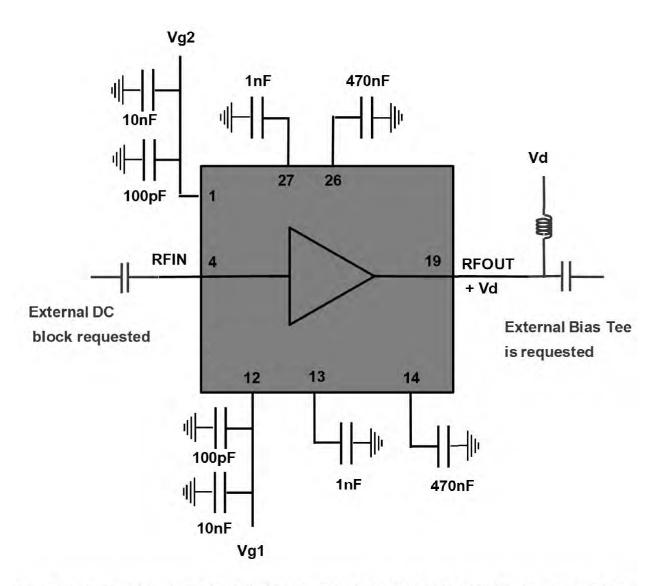

# **Application Circuit**

Note: external components are requested in order to use the part properly and to reach the presented performance data: on RF input access a DC block is requested, on RF output access a Bias Tee is requested.

Depending on the board, additional capacitors such as  $1\mu$ F may be added on Vg1 or Vg2 access if necessary, for better low frequency decoupling.

Smaller capacitors than 470nF could be use if the part is not use in low frequency range (< 1 GHz): 10nF.

# **Application Circuit**

Note: external components are requested in order to use the part properly and to reach the presented performance data: on RF input access a DC block is requested, on RF output access a Bias Tee is requested.

Depending on the board, additional capacitors such as  $1\mu$ F may be added on Vg1 or Vg2 access if necessary, for better low frequency decoupling.

Smaller capacitors than 470nF could be use if the part is not use in low frequency range (< 1 GHz): 10nF.

### **Pin Description**

| Pin                                              | Symbol      | Description                                                        |

|--------------------------------------------------|-------------|--------------------------------------------------------------------|

| 5, 18, 29 (exposed PAD)                          | GND         | Must be grounded properly, internal connections to ground are made |

| 2,3,6,7,8,9,10,15,<br>16,17,20,21,22,23,24,25,28 | NC          | No internal connections                                            |

| 4                                                | RF IN       | RF input, DC coupled to Vg1                                        |

| 12                                               | VG1         | Gate voltage, bias network required                                |

| 1                                                | VG2         | Gate voltage bias network required                                 |

| 19                                               | RF OUT + VD | RF output + Vd bias (see application circuit)                      |

| 13                                               | ACG4        | Low frequency termination4 on Vg1                                  |

| 14                                               | ACG3        | Low frequency termination3 on Vg1                                  |

| 26                                               | ACG2        | Low frequency termination2 on Vd                                   |

| 27                                               | ACG1        | Low frequency termination1 on Vd                                   |

Teledyne recommends to ground pins 2, 3, 6, 7, 11, 15, 16, 17, 20 and 21

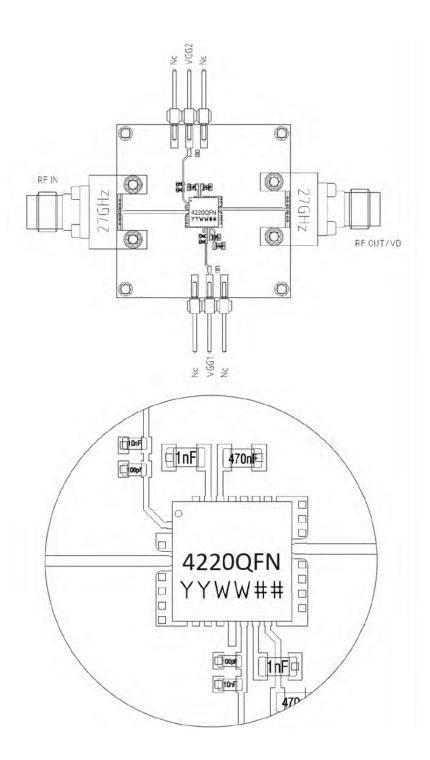

### **Evaluation Board**

- Based on typically Ro4003 / 8mils or equivalent.

- Using a micro-strip to coplanar transition to access the package.

- Recommended for the implementation of this product on a module board.

- Decoupling capacitors of 100 pF  $\pm5\%$  on Vg1 and Vg2 at first level; and 10 nF±10% at second level; additional 1  $\mu F$  capacitors on each Vg accesses.

- Low frequency terminations are closed on 1nF and 470 nF are recommended.

### **Device Operation**

### **Device Power Up instructions:**

- 1) Ground the device.

- 2) Set Vg1 to -1.5V.

- 3) Set Vd to 6.5V (nominal value for Vd).

- 4) Set Vg2 to 1.5V (nominal value for Vg2).

- 5) Set Vg1 in the range of -0.3V for having Idq=120mA.

- 6) Apply RF input power and adjust Vg2 to obtain desired gain.

### **Device Power Down instructions:**

- 1) Turn RF power supply off.

- 2) Set Vg1 to -1.5V in order to get Idq=0mA.

- 3) Set Vg2 to 0V.

- 4) Set Vd to 0V.

- 5) Set Vg1 to 0V.

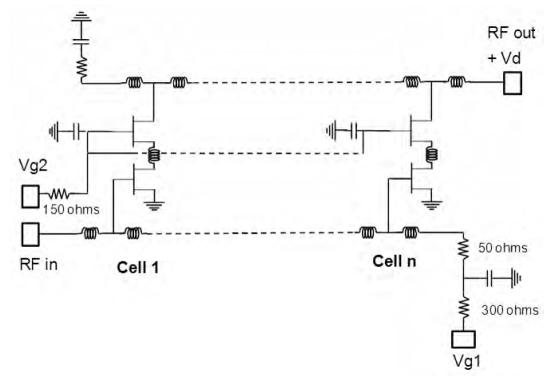

### **DC Schematic**

Vd = 6.5V, Vg1 = -0.3V, Vg2 = 1.5V, Idq = 120mA

### **Package Information**

| Parameter             | Values                                             |

|-----------------------|----------------------------------------------------|

| Package body material | RoHS-compliant Low stress injection Molded Plastic |

| Lead finish           | 100% matte-Tin (Sn)                                |

| MSL Rating            | MSL3                                               |

#### **Ordering Information**

| Order Code      | Description                                    | Package          | Shipping Method |

|-----------------|------------------------------------------------|------------------|-----------------|

| TDPA4220QFN     | Wideband Medium Power Amplifier                | 5 x 5 28-Pin QFN | Tape and Reel   |

| TDPA4220QFN-EVK | Wideband Medium Power Amplifier Evaluation Kit | Boxed            | Boxed           |

#### **Revision Information**

| Document                   | Description / Date       | Change/Revision Details |

|----------------------------|--------------------------|-------------------------|

| TDPA4220QFN-4-2024 Rev 0.2 | TDPA4220QFN / April 2024 | Initial Release         |

### **Document Categories and Definitions:**

#### **Advance Information**

The product is in a formative or design stage. The data sheet contains design target specifications for product development. Specifications and features may change in any manner without notice.

#### **Preliminary Specification**

The data sheet contains preliminary data. Additional data may be added at a later date. Teledyne e2v HiRel Electronics reserves the right to change specifications at any time without notice in order to supply the best possible product.

#### **Product Specification**

The data sheet contains final data. In the event Teledyne e2v HiRel Electronics decides to change the specifications, Teledyne e2v HiRel Electronics will notify customers of the intended changes by issuing a CNF (Customer Notification Form).

### **Sales Contact**

For additional information, Email us at: hirel@teledyne.com website: www.tdehirel.com

### **Disclaimers**

The information in this document is believed to be reliable. However, Teledyne e2v HiRel Electronics assumes no liability for the use of this information. Use shall be entirely at the user's own risk. No patent rights or licenses to any circuits described in this document are implied or granted to any third party. Teledyne e2v's products are not designed or intended for use in devices or systems intended for surgical implant, or in other applications intended to support or sustain life, or in any application in which the failure of the Teledyne e2v product could create a situation in which personal injury or death might occur. Teledyne e2v assumes no liability for damages, including consequential or incidental damages, arising out of the use of its products in such applications.

### **Copyright and Trademark**

Trademarks are the property of their respective owners.

©2024, Teledyne e2v HiRel Electronics. All rights reserved.